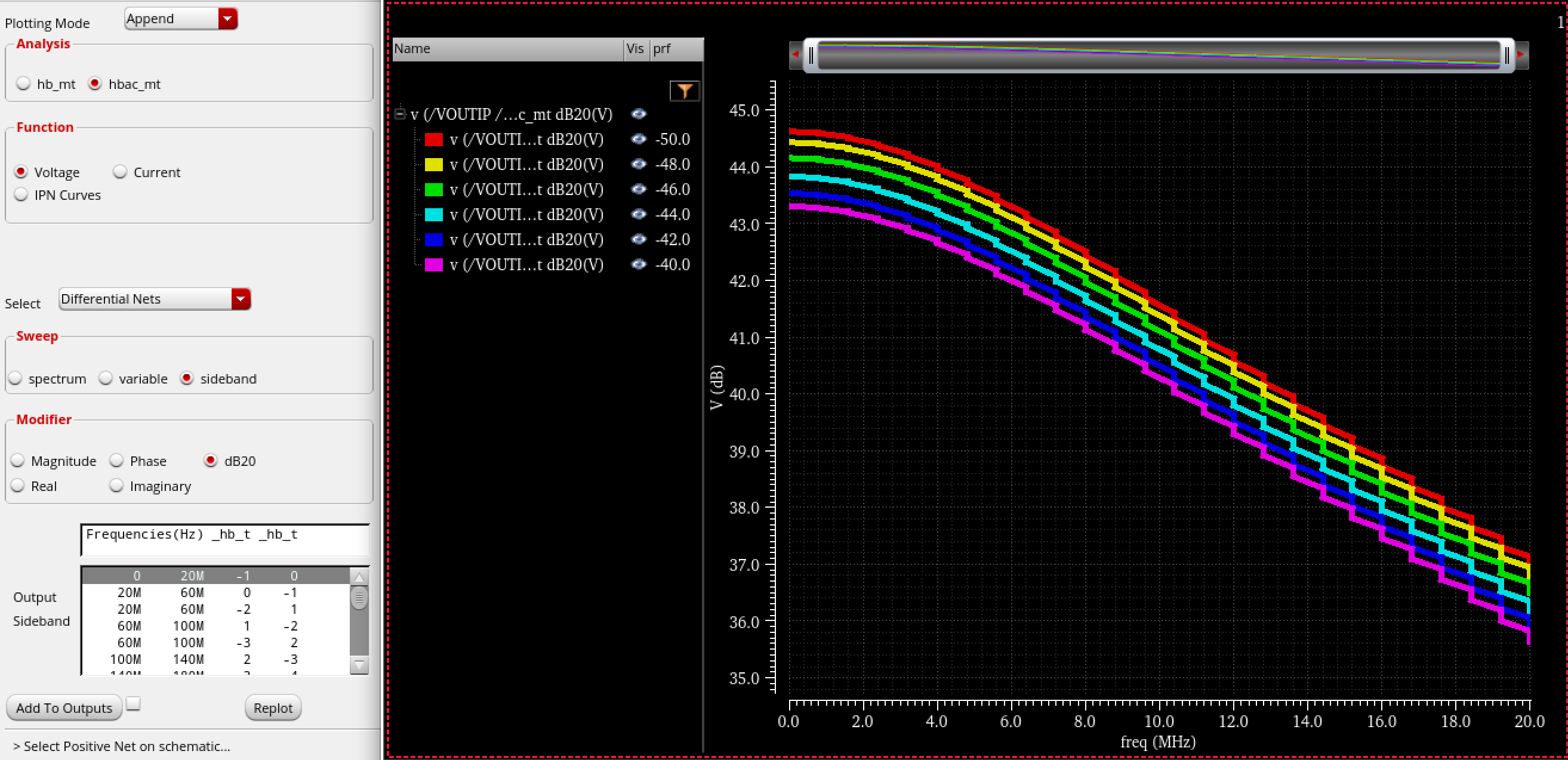

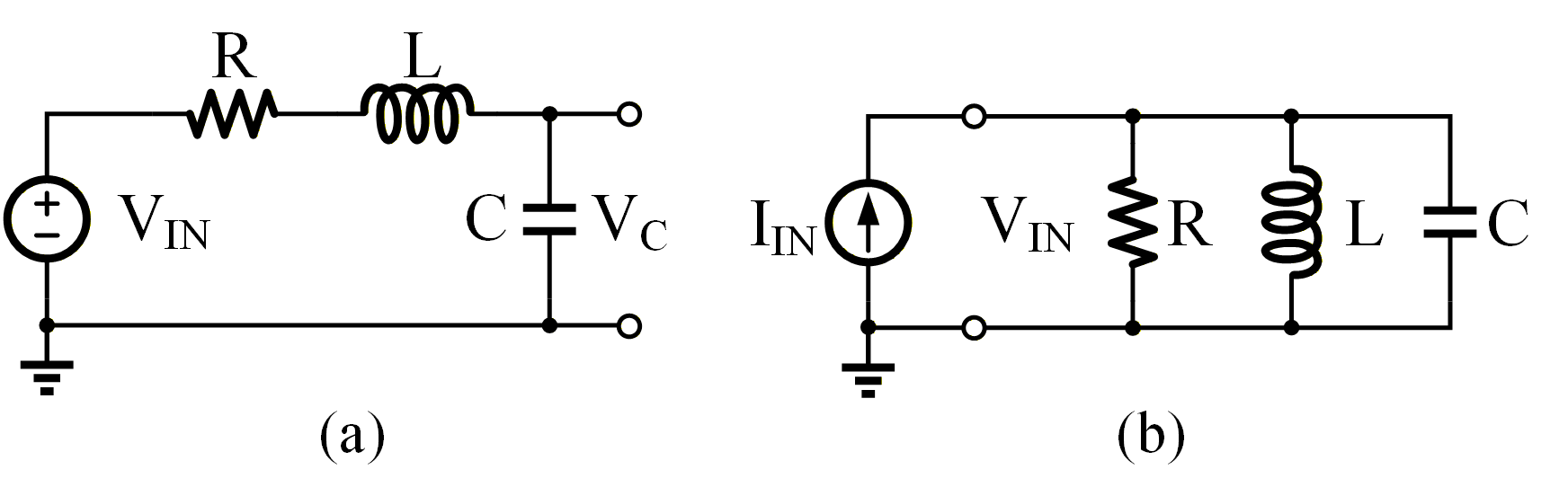

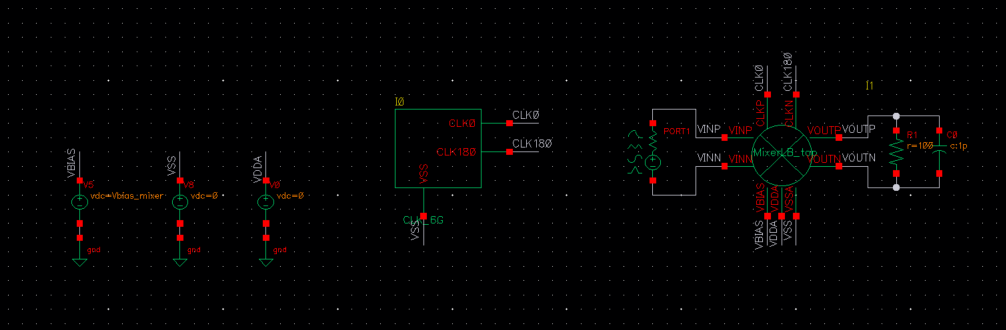

本文针对零中频接收机的仿真需求,介绍了一种通用的 Testbench 结构,并基于该结构系统介绍了转换增益、噪声系数、线性度(三阶交调点 IIP3)、二阶交调点(IIP2)、输入匹配(S11)、镜像抑制比(IRR)、Blocker 1dB 压缩点以及 Blocker 噪声系数共八项关键性能指标的仿真方法。通过设置变量(射频频率、功率、本振频率等),利用 Cadence HB 系列仿真器(HB、HBAC、HBNOISE、HBSP)即可在同一电路平台上灵活完成各项参数的评估。文中详细说明了每种仿真的定义、仿真器配置、变量设置以及后处理步骤,为射频接收机设计人员提供了一套清晰、可操作的仿真指南。

网站建站四周年纪念! 不知不觉又过了一周年。这一周年确实是没咋更新,但是最后成功憋了波大的,也算是完成了上周年期望的写一点电路原理介绍了。下一年预计会更新一到两篇文章吧,都是电路原理相关的。目前比较想写的一篇是关于反馈、稳定性和频率补偿的,但是这个涉及到的内容也非常多,预计至少得明年才可能正式发布了。这一年网站后台收到了很多评论,这里本人继续感谢大家在这一年的支持!

(更多…)

本文从RLC串并联谐振网络出发,系统梳理了谐振的定义、Q值与带宽的关系以及串联“短路”、并联“开路”等直观特性,并提出“三点法”快速分析电路幅频响应。随后深入二阶系统的标准形式与极点分布,借助向量图示法直观解释频域特性(如欠阻尼下的峰值与相移陡峭)和时域响应(超调、调节时间等关键指标)。最后展示如何将高阶系统分解为一阶与二阶子系统的级联,为滤波器、放大器等模拟电路设计提供了一套无需繁琐推导即可建立直觉的实用分析方法。

网站建站三周年纪念日! 一转眼就三周年了啊。三年前,本人刚买服务器的三年学生优惠并开始建站的时候还在想,自己三年后已经到博士中期了,那时候会怎么样呢。没想到三年过去的这样快,不过幸好目前也算是小有收获了。去年一年因为太忙,网站更新的着实不多。下一年可能也不会有时间写太多文章,但是会继续坚持更新的,同时文章也准备向着电路原理的介绍的方向转变了。本人在这里感谢大家一直以来的支持,希望大家能继续关注。

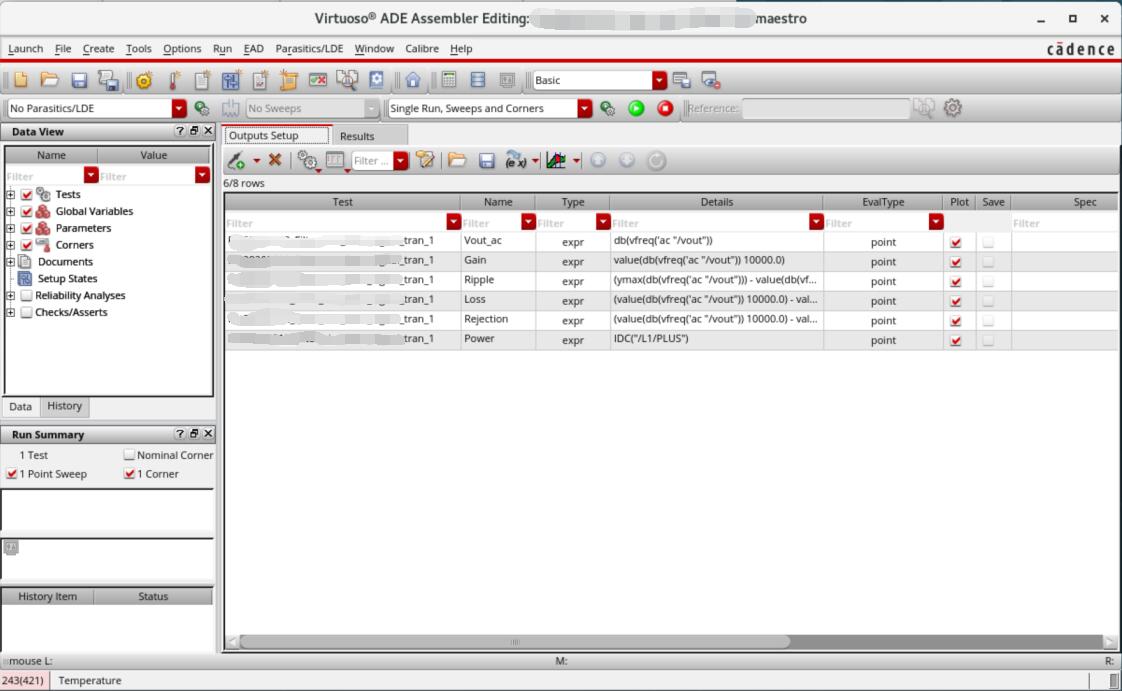

在模拟集成电路设计中,对电路进行仿真是评估电路能否正常工作以及获知电路的具体性能参数的一个重要的方式。而对于一个特定的模拟电路结构而言,通常会存在数种不同的性能参数来描述电路的具体工作特性,并且某些电路中还会具有一些数字单元需要控制,此外在流片前通常还需要进行一些诸如工艺角和蒙卡之类的的仿真。对于一个模拟电路而言,通常需要运行数种不同的仿真才后才能对电路性能有一个比较全面的了解。这就导致该领域的新人在刚刚掌握仿真器的用法后,会对一个一个运行这数种仿真感到恐惧,同时一个一个运行也会导致大量的时间浪费。这就需要找到一种能够快速并行的运行多种不同类型的仿真的操作方式,从而解放人的手工劳动,减少时间的浪费,将宝贵的时间利用在电路设计中去。本文将主要针对这一问题,介绍 Cadence Virtuso 中 maesrto 仿真平台下的快速仿真方法,从而达到白天配置仿真—>晚上服务器跑仿真->第二天「收菜」(获取并整理仿真结果)的高效仿真模式。

在进行集成电路设计时,通常会遇到需要使用其他公司的 IP 核的情况(例如需要使用 SRAM)。为了保密,这些 IP 核很可能不包含原理图,只包含一个可以应用的版图以及一些必要的用于支持 Cadence 或者 Symopsys 的仿真文件和库文件(例如 Verilog 或者 Verilog-A)等等。 对于这种模块,如何过版图的 LVS 就成了一个需要考虑的问题。

对于这类 IP 核,通常库中还会提供一些用于验证 LVS 的文件,例如网表文件等等。多数情况下这些网表文件是可以被成功导入 Cadence Virtuoso 中去的,但是也存在少量情况下无法导入到 Cadence Virtuoso。这里本人将针对这两种情况,来分别描述一下该如何使用该网表文件验证版图的 LVS。

网站建站两周年纪念日! 不知不觉这个网站已经运行两周年了,我会尽力让它一直运行下去,并坚持去写一些可能有意义的内容的,谢谢大家支持。

1 前言 不知道大家是否遇到过这种情况:在对接收机或者发射机进行仿真时,由于芯片中的时钟产生为一个 PLL,该 PLL 电路结构较为复杂,并且通常需要经过大量的时间才能够锁定,从而才能够产生我们所期望的时钟信号。但是,对于收发机而言,时钟信号是一个非常关键的信号,只有时钟信号正常产生后收发系统才能够正常工作。因此,在对整体系统进行仿真时,往往由于这…

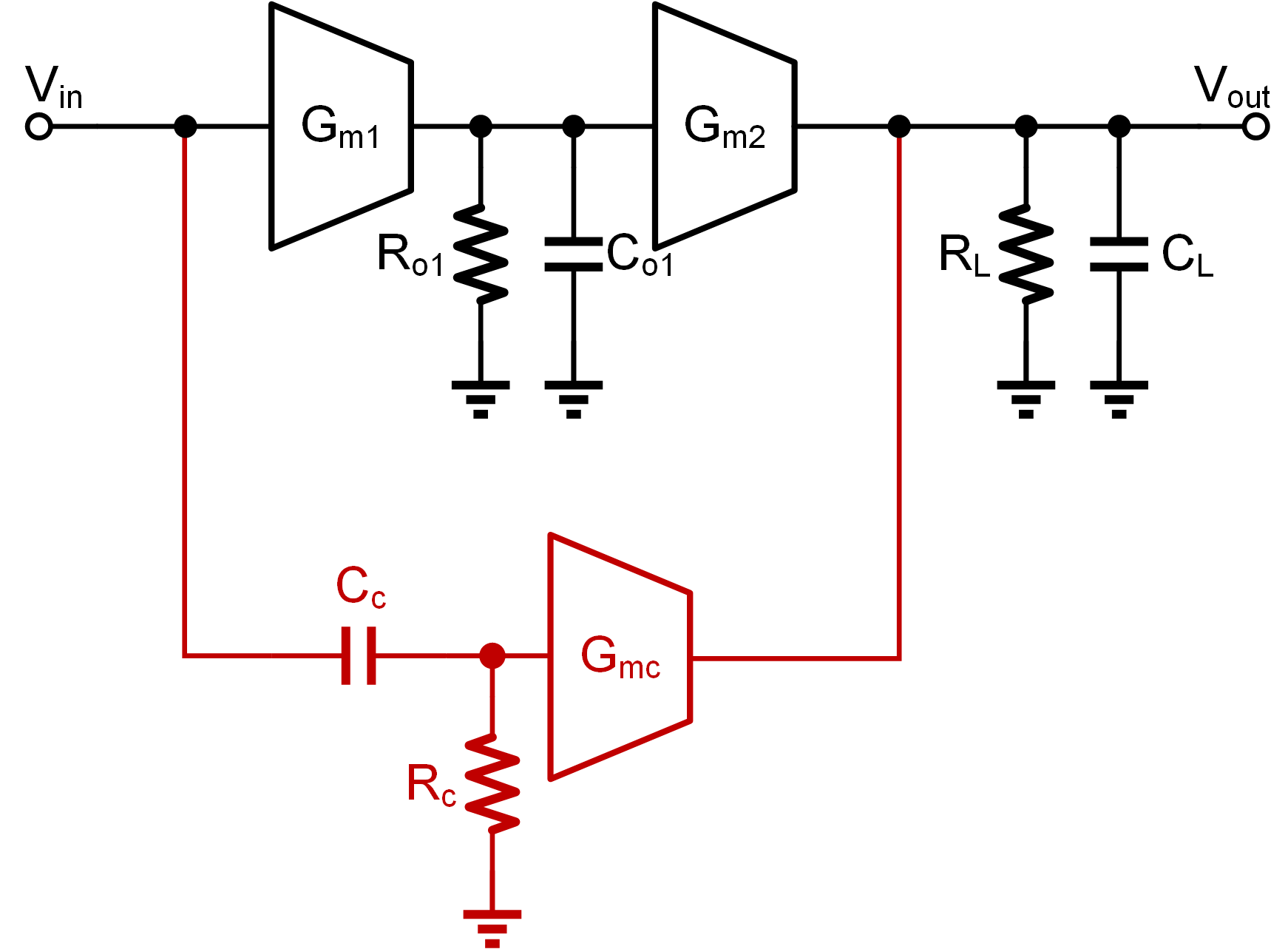

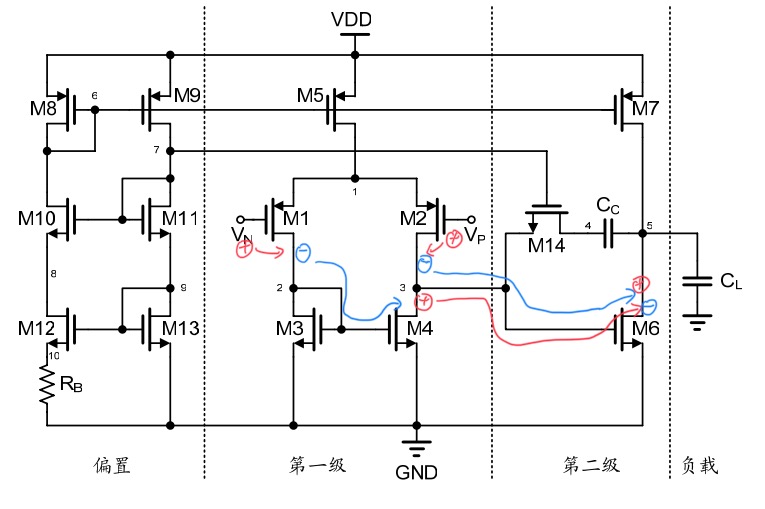

随着集成电路技术的迅猛发展,特别是纳米级工艺的实现,跨导运算放大器朝着高增益、高带宽以及低功耗的方向发展,其信号处理的能力也在不断的提高。但是目前 OTA 仍然是制约模拟电路 IC 设计的一个瓶颈。作为模拟电路的一个基本单元,OTA 电路需要具有一个较宽的带宽和一个较高的直流增益。但是在实际的电路设计中,这两个指标通常是相互矛盾的,并且被有限的跨导、较小的输出电阻以及较低的偏置电压限制。

一个单端的运算放大器通常会包含一个正输入端、一个负输入端和一个输出端。通常情况下,一个单端运放的输出端都是固定的,并且非常容易判断。但是在确定好输出端之后,对于运放的两个输入端,是不能按照自己的心情去随心所欲的标注的,而是需要对其进行判断,来确定哪个是正输入端哪个是负输入端。一旦正负输入端标错,就会造成运放外部电路由原来的负反馈变为正反馈,从而导致电路工作状态的异常。而对于全差分放大器,则存在正负输入端和正负输出端的判断为问题,如果判断失误同样会导致电路的工作异常。因此,正确判断运放的正负输入端是十分重要的。这里,本人将通过举例子的方式,来说明一下运放的正负输入端的判断方法。