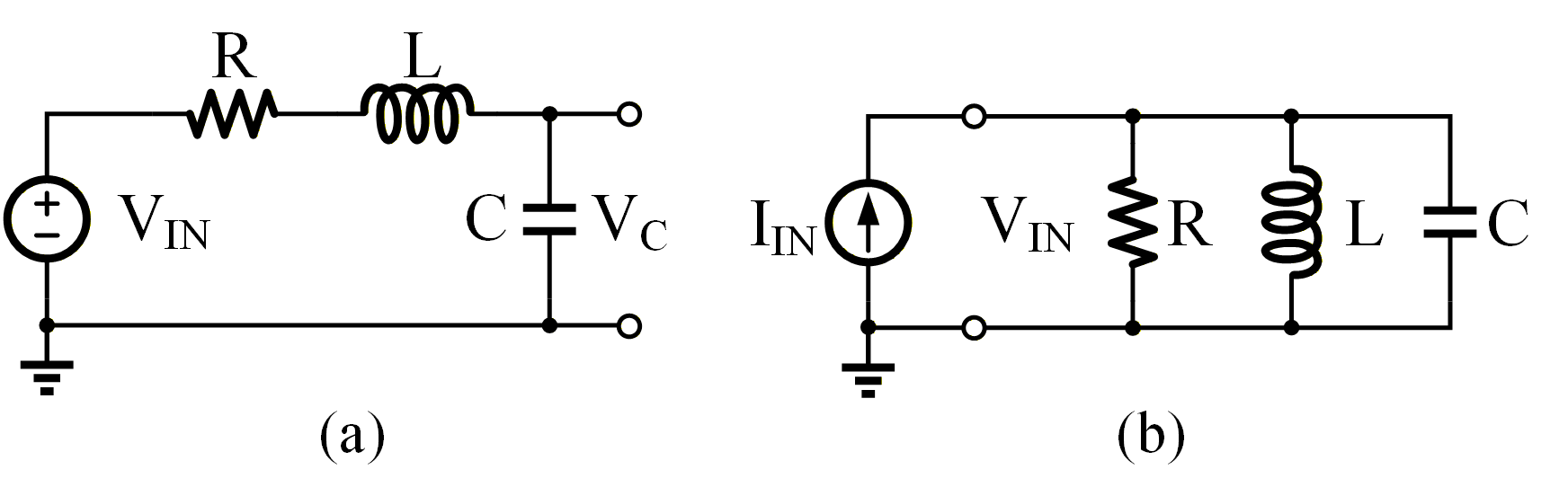

本文从RLC串并联谐振网络出发,系统梳理了谐振的定义、Q值与带宽的关系以及串联“短路”、并联“开路”等直观特性,并提出“三点法”快速分析电路幅频响应。随后深入二阶系统的标准形式与极点分布,借助向量图示法直观解释频域特性(如欠阻尼下的峰值与相移陡峭)和时域响应(超调、调节时间等关键指标)。最后展示如何将高阶系统分解为一阶与二阶子系统的级联,为滤波器、放大器等模拟电路设计提供了一套无需繁琐推导即可建立直觉的实用分析方法。

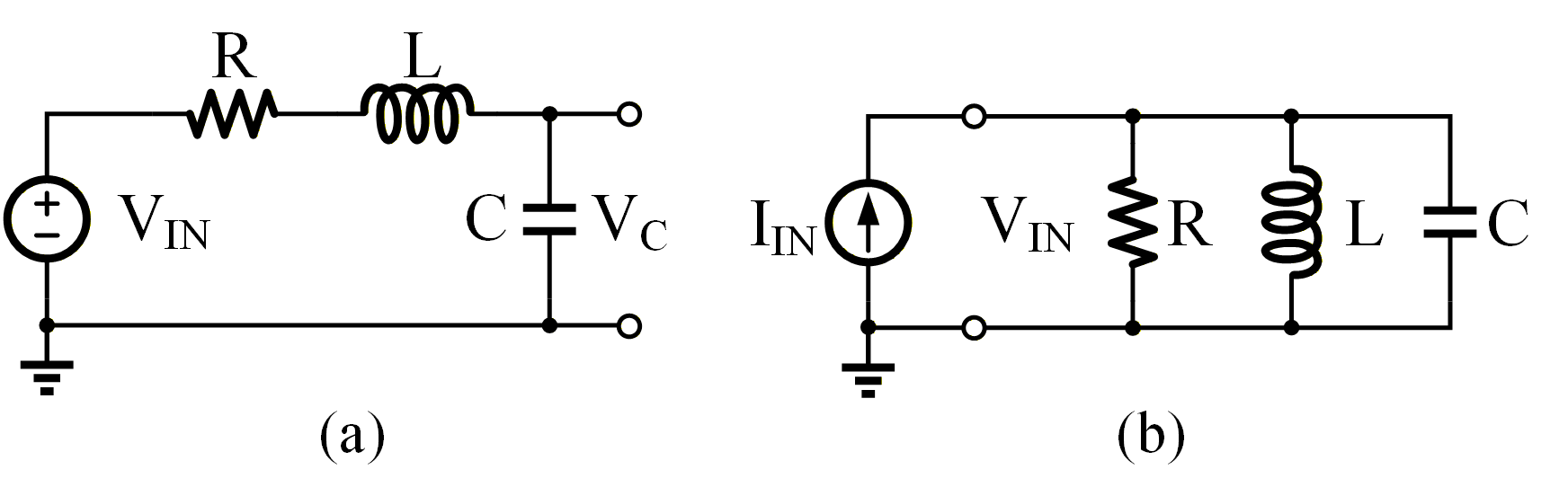

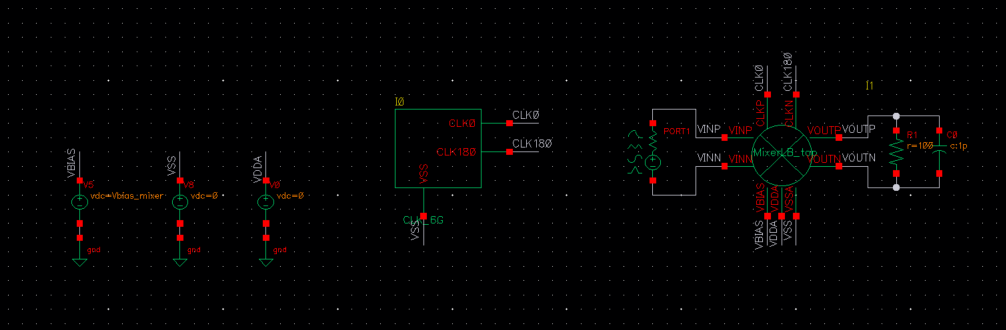

1 前言 不知道大家是否遇到过这种情况:在对接收机或者发射机进行仿真时,由于芯片中的时钟产生为一个 PLL,该 PLL 电路结构较为复杂,并且通常需要经过大量的时间才能够锁定,从而才能够产生我们所期望的时钟信号。但是,对于收发机而言,时钟信号是一个非常关键的信号,只有时钟信号正常产生后收发系统才能够正常工作。因此,在对整体系统进行仿真时,往往由于这…

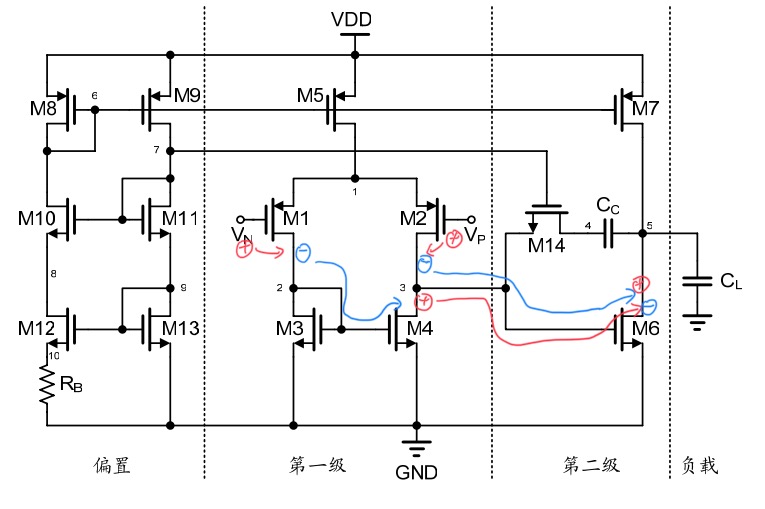

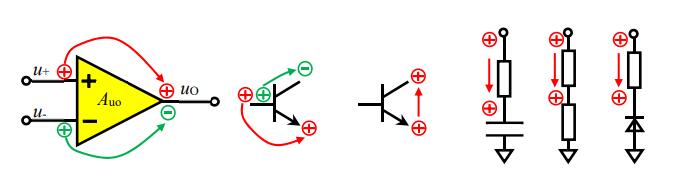

一个单端的运算放大器通常会包含一个正输入端、一个负输入端和一个输出端。通常情况下,一个单端运放的输出端都是固定的,并且非常容易判断。但是在确定好输出端之后,对于运放的两个输入端,是不能按照自己的心情去随心所欲的标注的,而是需要对其进行判断,来确定哪个是正输入端哪个是负输入端。一旦正负输入端标错,就会造成运放外部电路由原来的负反馈变为正反馈,从而导致电路工作状态的异常。而对于全差分放大器,则存在正负输入端和正负输出端的判断为问题,如果判断失误同样会导致电路的工作异常。因此,正确判断运放的正负输入端是十分重要的。这里,本人将通过举例子的方式,来说明一下运放的正负输入端的判断方法。

在我本科的模电课上,杨老师曾经教过我们一种判断环路反馈极性的简单方法。在本人之后面对过的关于判断反馈环路的极性的问题中,这种方法屡试不爽,并且它可以毫无修改的应用在模拟集成电路中。由于这种方法在判断反馈环路的极性时十分简洁好用,因此这里本人开了一篇文章,来介绍一下这种方法。

在此之前,本人已经学习到过很多结构的 Q 值。在这些学习过程中,存在着一个困扰了本人许久的问题:为什么对于同一个被叫做「Q 值」的东西,在不同的情况下竟然有这么多种看似完全不相干的定义方式?最近,本人对各种结构的 Q 值的定义以及计算公式进行了一番思考和整理,以期能够找到这些 Q 值之间的联系。最终发现,这些 Q 值或多或少的都能够与「二阶系统的传递函数」扯上关系。

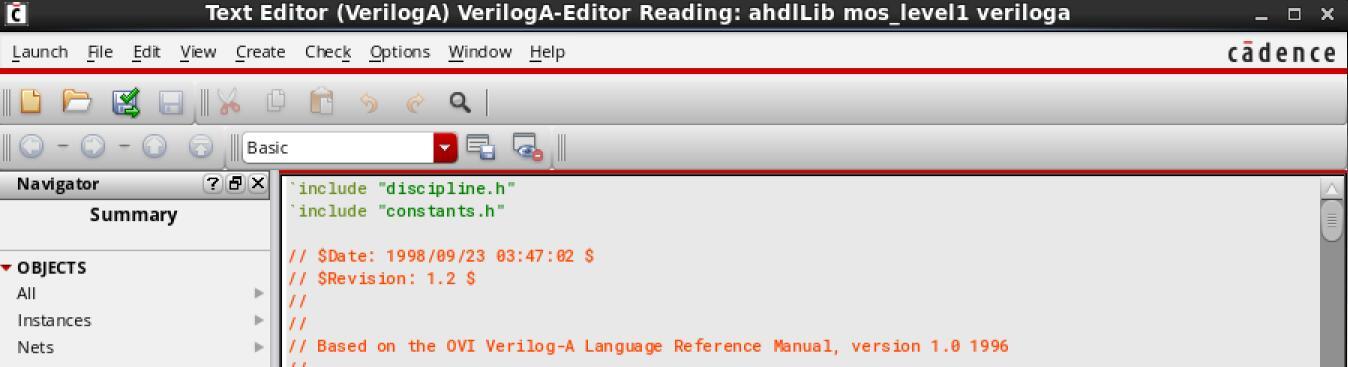

目前,国内网站上关于 Verilog-A 的信息非常的少,并且关于该语言常用的几个参考文档也都是英文文档。本人在学习这个语言的时候,曾经花费了非常多的时间来阅读文档、学习语法。但是学习之后发现,Verilog-A 的语法和 Verilog HDL 极其相似,因此写了这一篇文章,希望能帮到一些要学习 Verilog-A 的人。