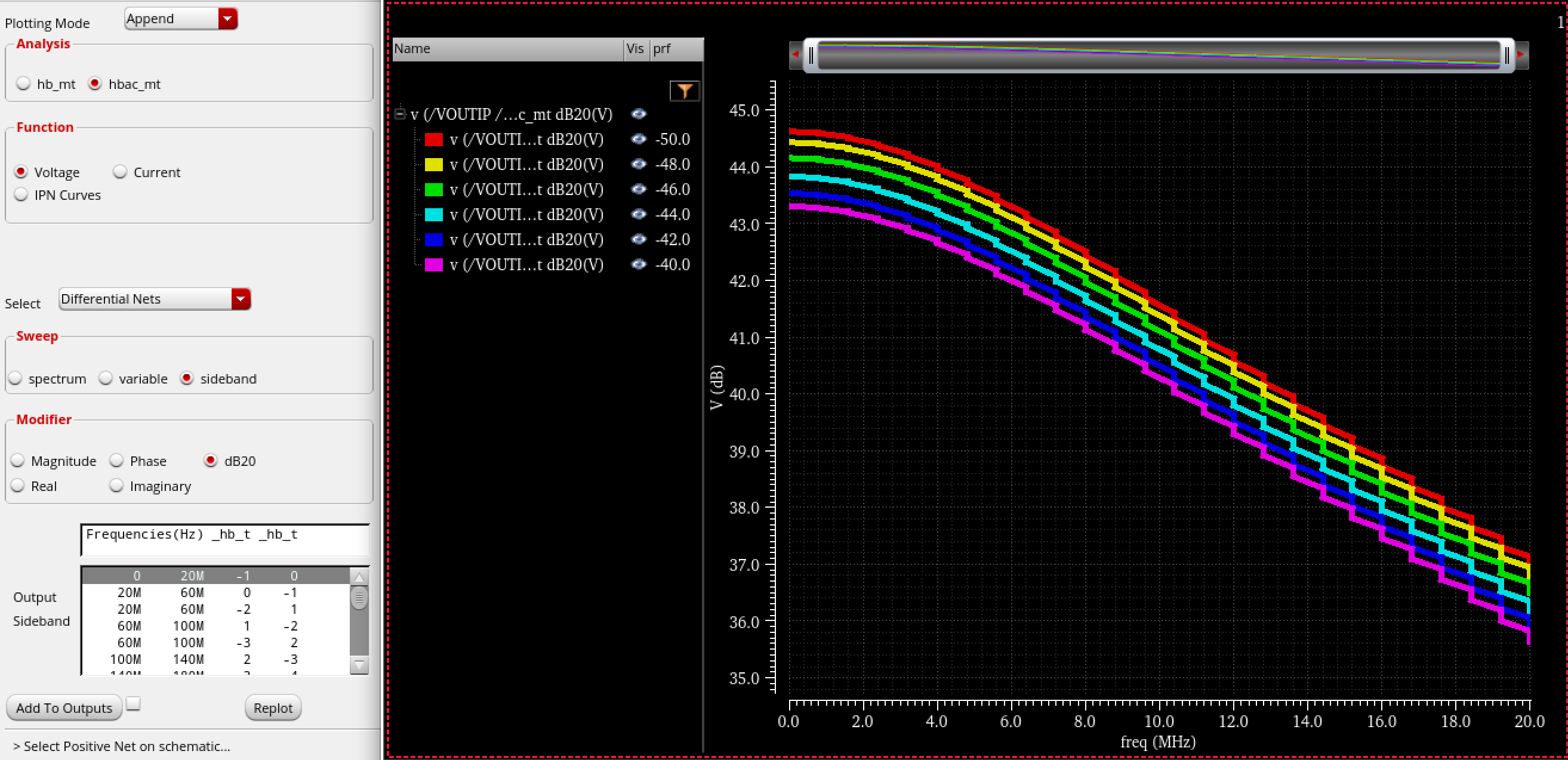

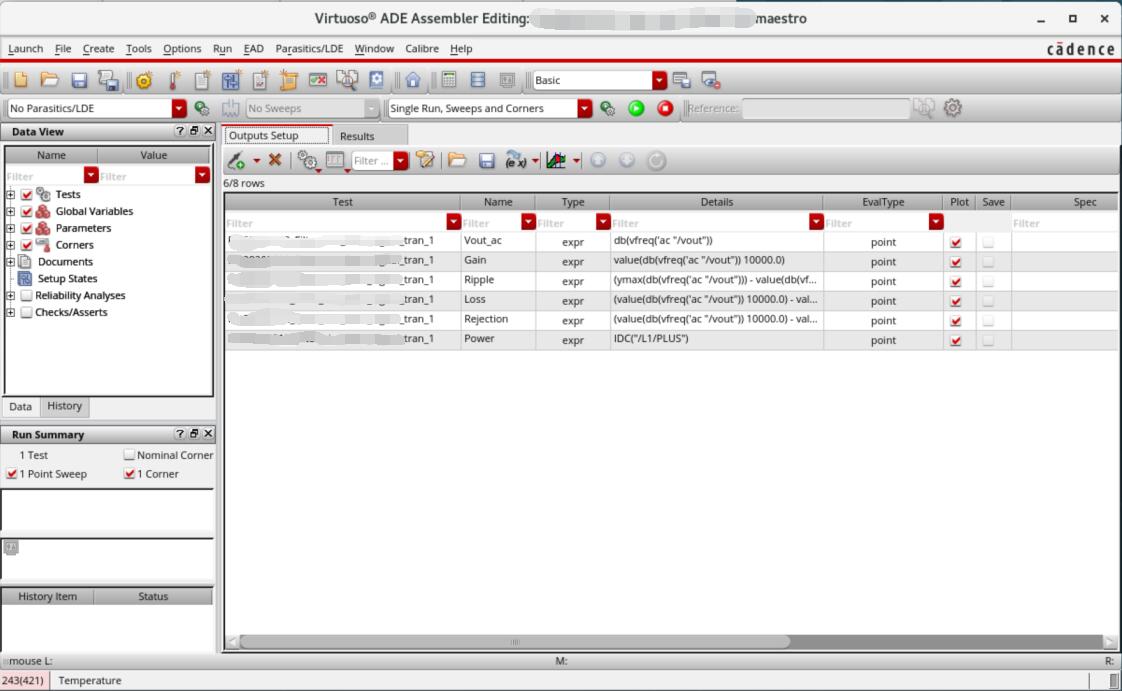

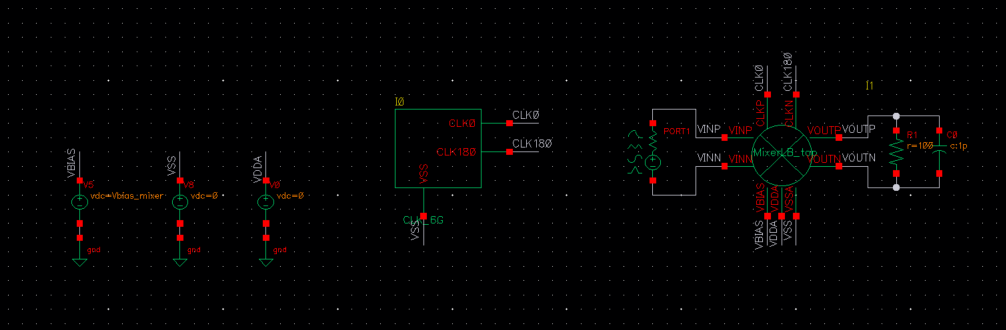

本文针对零中频接收机的仿真需求,介绍了一种通用的 Testbench 结构,并基于该结构系统介绍了转换增益、噪声系数、线性度(三阶交调点 IIP3)、二阶交调点(IIP2)、输入匹配(S11)、镜像抑制比(IRR)、Blocker 1dB 压缩点以及 Blocker 噪声系数共八项关键性能指标的仿真方法。通过设置变量(射频频率、功率、本振频率等),利用 Cadence HB 系列仿真器(HB、HBAC、HBNOISE、HBSP)即可在同一电路平台上灵活完成各项参数的评估。文中详细说明了每种仿真的定义、仿真器配置、变量设置以及后处理步骤,为射频接收机设计人员提供了一套清晰、可操作的仿真指南。

在模拟集成电路设计中,对电路进行仿真是评估电路能否正常工作以及获知电路的具体性能参数的一个重要的方式。而对于一个特定的模拟电路结构而言,通常会存在数种不同的性能参数来描述电路的具体工作特性,并且某些电路中还会具有一些数字单元需要控制,此外在流片前通常还需要进行一些诸如工艺角和蒙卡之类的的仿真。对于一个模拟电路而言,通常需要运行数种不同的仿真才后才能对电路性能有一个比较全面的了解。这就导致该领域的新人在刚刚掌握仿真器的用法后,会对一个一个运行这数种仿真感到恐惧,同时一个一个运行也会导致大量的时间浪费。这就需要找到一种能够快速并行的运行多种不同类型的仿真的操作方式,从而解放人的手工劳动,减少时间的浪费,将宝贵的时间利用在电路设计中去。本文将主要针对这一问题,介绍 Cadence Virtuso 中 maesrto 仿真平台下的快速仿真方法,从而达到白天配置仿真—>晚上服务器跑仿真->第二天「收菜」(获取并整理仿真结果)的高效仿真模式。

在进行集成电路设计时,通常会遇到需要使用其他公司的 IP 核的情况(例如需要使用 SRAM)。为了保密,这些 IP 核很可能不包含原理图,只包含一个可以应用的版图以及一些必要的用于支持 Cadence 或者 Symopsys 的仿真文件和库文件(例如 Verilog 或者 Verilog-A)等等。 对于这种模块,如何过版图的 LVS 就成了一个需要考虑的问题。

对于这类 IP 核,通常库中还会提供一些用于验证 LVS 的文件,例如网表文件等等。多数情况下这些网表文件是可以被成功导入 Cadence Virtuoso 中去的,但是也存在少量情况下无法导入到 Cadence Virtuoso。这里本人将针对这两种情况,来分别描述一下该如何使用该网表文件验证版图的 LVS。

1 前言 不知道大家是否遇到过这种情况:在对接收机或者发射机进行仿真时,由于芯片中的时钟产生为一个 PLL,该 PLL 电路结构较为复杂,并且通常需要经过大量的时间才能够锁定,从而才能够产生我们所期望的时钟信号。但是,对于收发机而言,时钟信号是一个非常关键的信号,只有时钟信号正常产生后收发系统才能够正常工作。因此,在对整体系统进行仿真时,往往由于这…

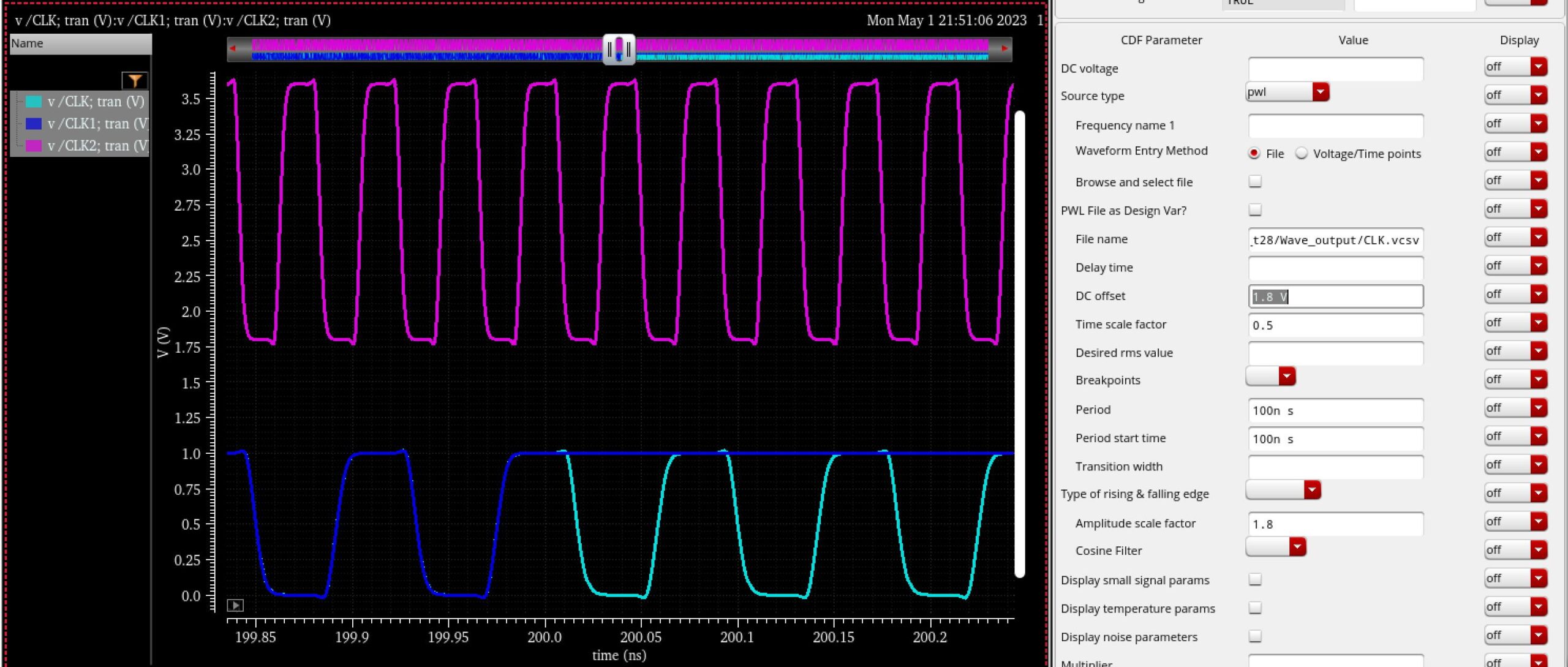

也许大家有时候在仿真中可能会遇到这样的情况:某些时候我们需要对一个系统进行时域仿真,而这个系统中却偏偏存在一个类似 PLL 之类的时钟电路。如果将这个时钟电路替换为理想的时钟源或者是使用这个时钟在稳定状态时的输出,那么只需要跑几百纳秒即可获得正确的系统输出结果。但是由于这个时钟的存在,系统仿真时往往需要等待相当长的时间,以使得时钟的输出稳定下来,这样在系统级的后仿中,会极大拖长仿真运行的时间,降低效率。因此,假设如果我们能够只进行一次这样的相当长时间的仿真,并且将此时时钟电路输出的稳态波形保存起来,提供给后续的电路仿真使用,这样就能在几乎不损失精度的情况下极大的提升仿真的速度。而这就是本文接下来要描述的一种仿真方法。

数模混和仿真,顾名思义,就是能够将数字电路和模拟电路混合在一起,进行电路的仿真的一种仿真方法。由于现在的模拟或者射频电路中通常会包含一定的数字电路成分,例如用来读出数据和控制数字修调的通信接口电路(如 SPI 电路)等等,因此在对这类电路的功能进行仿真验证时,往往需要使用一些数字类型的激励文件(例如 Verilog 写成的 Testbench)来对系统进行仿真;这时候,就需要进行数模混合仿真了。

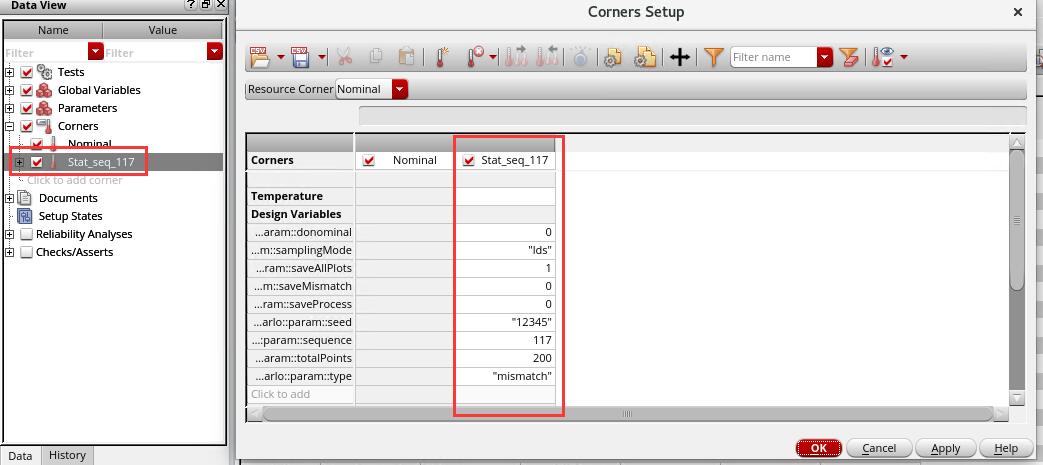

之前的一篇文章中提到,在蒙特卡洛仿真中可以通过设置不考虑某些器件的失调的方式来分析一个电路中的某些器件对电路失调特性的影响。此外,Cadence 的蒙特卡洛仿真中还提供一个功能:将一次蒙特卡洛仿真中的一个具体的点创建成一个静态的 Corner,这个 Corner 会记录这一次蒙特卡洛仿真的信息。有了这一个静态的 Corner 后,我们就可在这个静态的 Corner 下运行 DC、AC、PSS以及 HB 等多种仿真分析,来全面分析一个电路在当前失调情况下的各项性能指标并寻找改进方法。

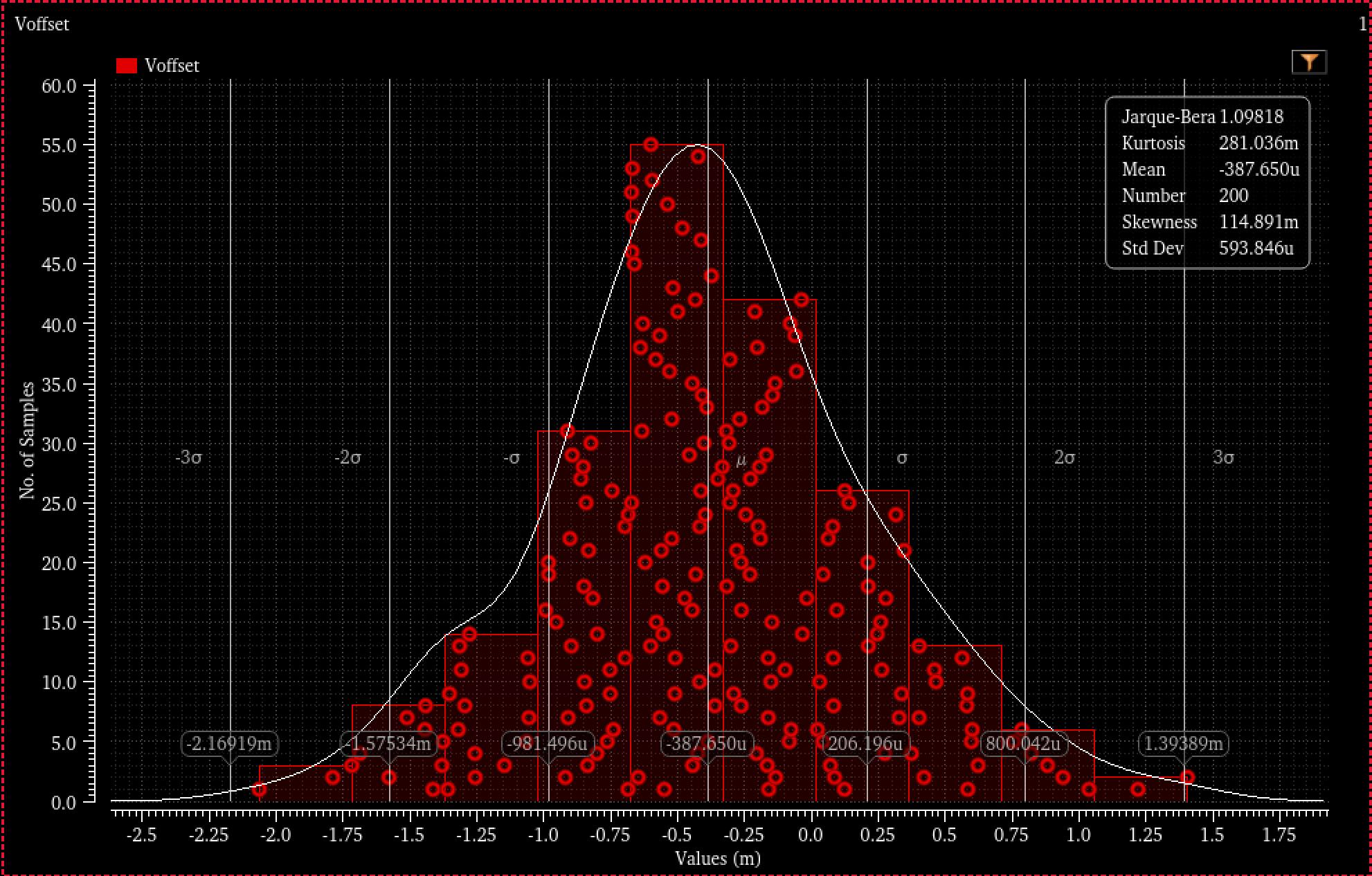

在涉及到需要对工艺的失配情况进行分析时,往往需要用到蒙特卡洛仿真。蒙特卡洛仿真可以较好的分析出电路在不同工艺失配情况下的工作情况。但是,当运行蒙特卡洛仿真后,有时可能会发现由于失配的影响,导致某一项关心的电路的性能参数很差,或者有了较大的恶化,这时候可能就需要分析是哪部分器件或者电路成分引起了性能的恶化。这时,就可以利用 Cadence 蒙特卡洛仿真设置中的一个功能——设置在进行仿真时不考虑某些器件的失调。

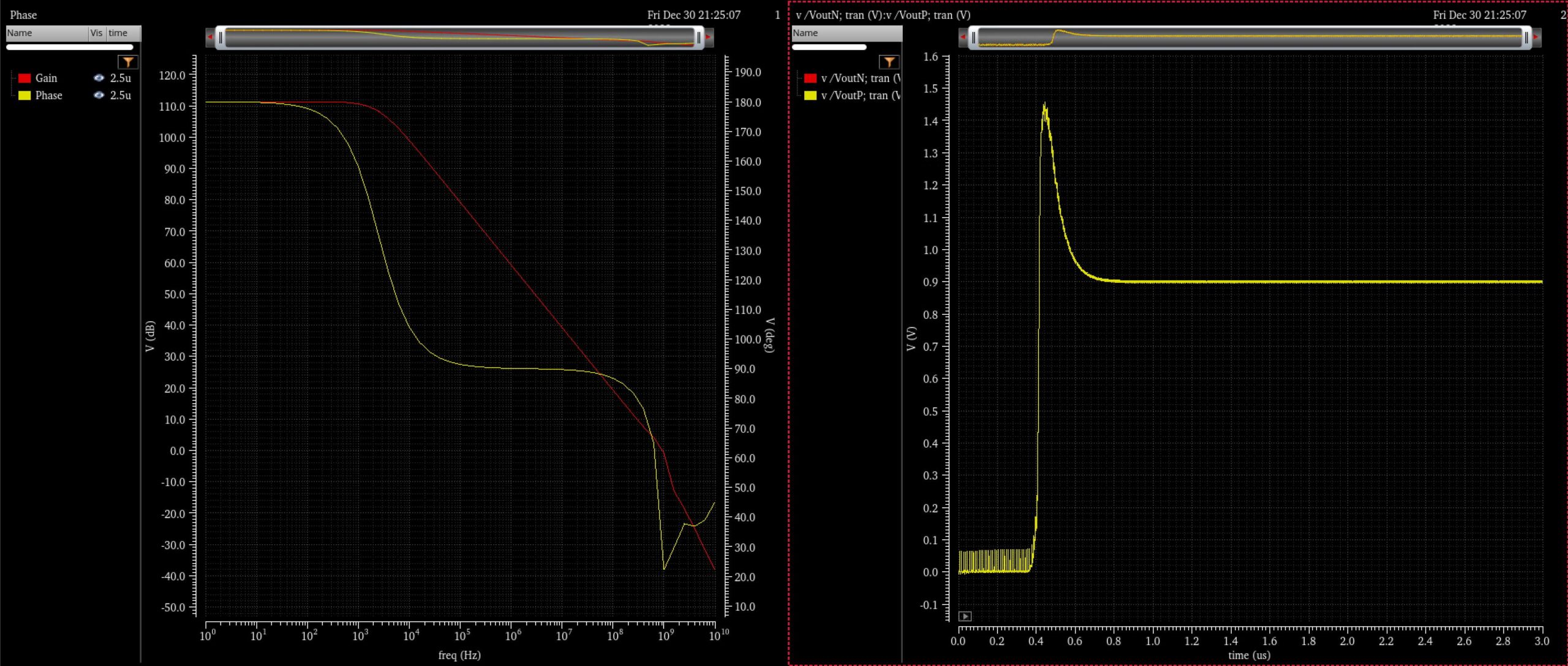

在对全差分放大电路进行设计时,可能会使用到开关电容共模反馈,如下图。由于开关电容共模反馈需要一定的时间来将输出电压稳定到共模电压,而普通的 AC 仿真是默认使用 DC 时的工作点来进行 AC 特性计算的,此时运放的输出还并未稳定到共模电压上,因此此时使用 AC 仿真计算的结果会与实际运放的增益有较大的偏差。一种可行的解决方案为先对该放大器电路进行时域(TRAN)仿真,并且通过对 TRAN 仿真进行设置,使用 TRAN 仿真中的某一个时刻的 TRAN 工作点(Transient Operating Points)来对运放的 AC 特性进行仿真。

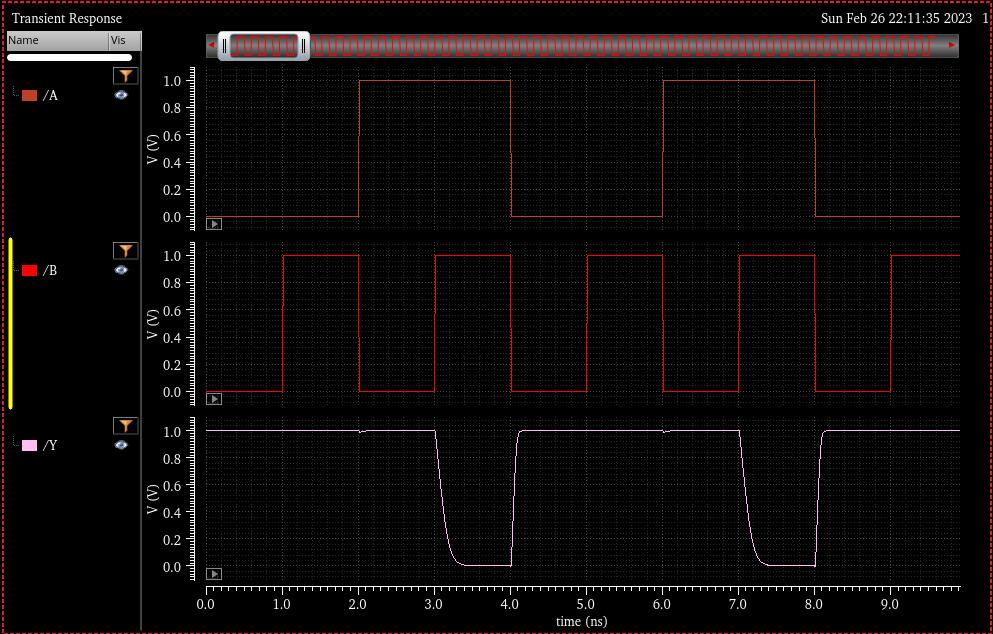

本站之前的一篇文章中简单的介绍了一下使用 Cadence IC617 中的蒙特卡洛仿真器来仿真单端运放的失调电压的方法,同时还放出了那个示例运放的失调电压仿真结果。这篇文章将简要的介绍一下斩波运放,以及如何仿真斩波运放的等效输入失调电压。