1 前言

数模混和仿真,顾名思义,就是能够将数字电路和模拟电路混合在一起,进行电路的仿真的一种仿真方法。由于现在的模拟或者射频电路中通常会包含一定的数字电路成分,例如用来读出数据和控制数字修调的通信接口电路(如 SPI 电路)等等,因此在对这类电路的功能进行仿真验证时,往往需要使用一些数字类型的激励文件(例如 Verilog 写成的 Testbench)来对系统进行仿真;这时候,就需要进行数模混合仿真了。

2 AMS 数模混仿前的准备

Cadence 中有一种能够用来做混合信号的仿真器,叫做 AMS 仿真器。AMS 仿真器现在被包含在 XCELIUM 中,它的原型是 INCISIV,一些古早版本的 Cadence 可能还在使用 INCISIV 这个软件来进行仿真。本次教程将以一个与非门电路为例介绍一下使用 AMS 仿真器进行数模混仿的流程。

2.1 准备好要仿真的模拟电路

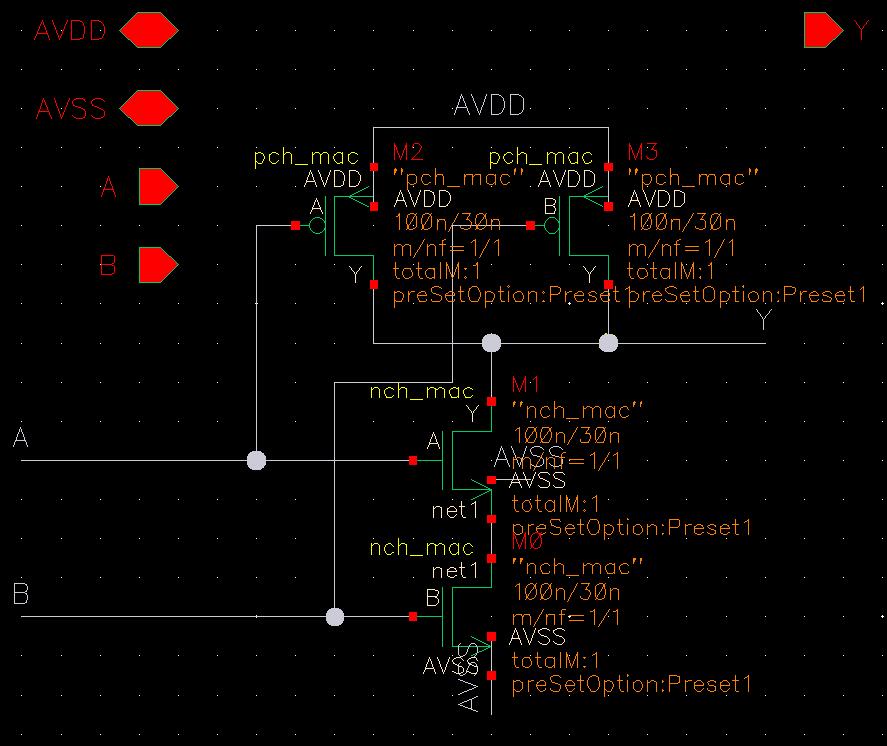

要进行混合信号仿真,肯定是需要有一个模拟电路来进行仿真的,这里本人准备了一个用 MOS 晶体管搭建而成的两输入与非门电路来进行接下来的数模混合仿真,如下图:

2.2 准备一个数字电路的代码文件

既然要进行数模混仿,同时也需要有一个数字电路。所以在进行仿真前需要新建一个数字电路的代码文件。这个代码文件可以是接下来要进行综合的电路,也可以是一个 Testbench 文件。在 Cadence 中,建立一个数字代码文件的方式和建立一个普通的 schematic 文件类似,同样是通过 「File – New – Cellview」的方式进行建立,如下图:

随后,在弹出的窗口内将「Type」选为「Verilog」,并且设置好新建的 verilog 文件的名称,即可新建一个 verilog 文件了,如下图:

本次教程使用的 Verilog 文件只是一个简单的示例,因此这里就只是简单的写几句话来为与非门施加一个激励波形。仿真使用的 verilog 代码为:

/Verilog HDL for "Amp_forweb", "nand_tb" "functional"

`timescale 1ns/1ns

module nand_tb (

output reg A, B

);

initial begin

A = 0;

B = 0;

end

always begin

#2 A = ~A;

end

always begin

#1 B = ~B;

end

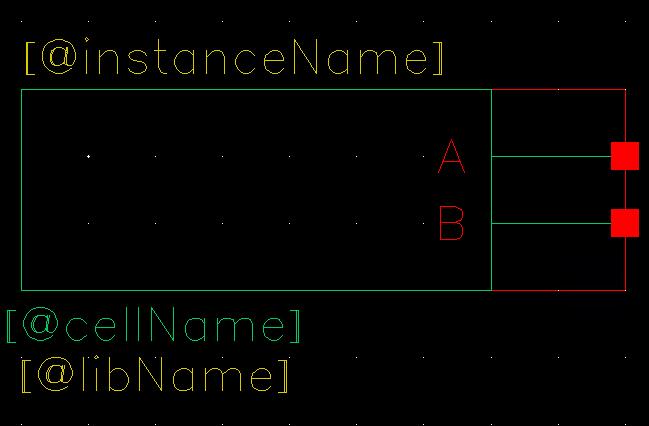

endmodule写完后,将这个代码保存并编译,如果写的没有问题的话这时就会弹出一个提示框,问你是否创建一个 symbol,这时候点击创建就可以了。上面那个代码最终创建好的 symbol 长这个样:

2.3 创建好用来进行仿真的 Testbench

在对电路进行数模混仿时,需要创建一个 Testbench,来将模拟电路和数字代码连接起来仿真。创建 Testbench 的方法和前文几乎相同,同样是使用「File – New – Cellview」选项,并在弹出的窗口内将「Type」选为「schematic」即可。随后就可以搭建 Testbench 了。本人搭建的 Testbench 如下图所示:

绘制完成后不要忘记点击「check and save」。

2.4 在「cds.lib」中添加数模混仿需要用到的链接库

在本人所使用的环境中,要想进行数模混仿,还需要添加一个链接库,用来支持数模混仿的进行。具体的添加方式为在自己的「cds.lib」中添加这样一行文字并且重启 Cadence(或者使用 Cadence Library Manager 中的 「View->Refresh」功能):

DEFINE connectLib /...(此处需要填写你自己的服务器中 XCELIUM 所在的按照 路径)/XCELIUM21.09.011/tools/affirma_ams/etc/connect_lib/connectLib或者也可以直接在 Cadence Library Manager 中使用「Edit->Library Path」功能将该库导入。

3 AMS 数模混仿的流程

3.1 新建 config 文件

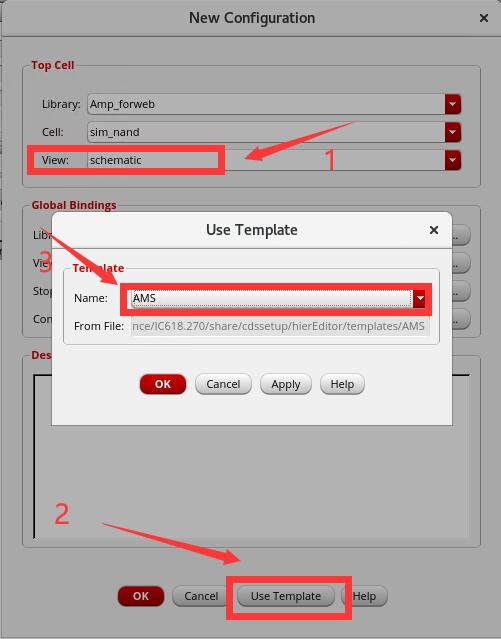

在进行数模混仿时,首先需要建立一个 config 文件,以便仿真器自行配置仿真环境。建立该文件的方法为:点击「File – New – Cellview」,并在弹出窗口中将「Cell」设置为上文中 Testbench 的名字,并将「Type」选为「config」即可,如下图:

随后,在弹出的 config 文件中,需要将「View」设置成「schematic」,并选择「Use Template」,随后将「Name」选择为「AMS」,点击 OK 即可。

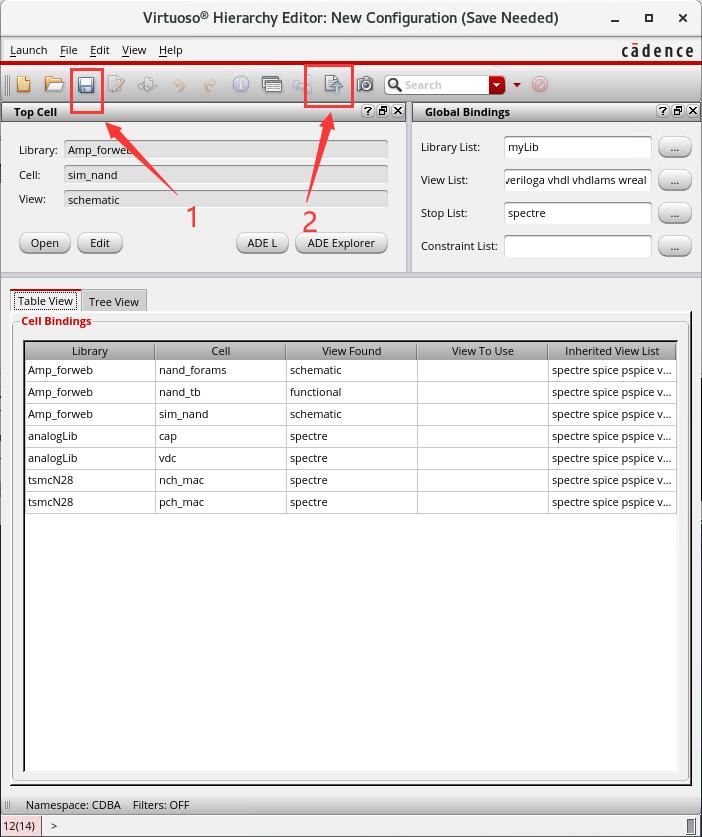

设置好后,点击一下保存,并点击一下上传,这个 config 文件就算是建立好了,如下图:

3.2 新建 maestro 文件进行仿真

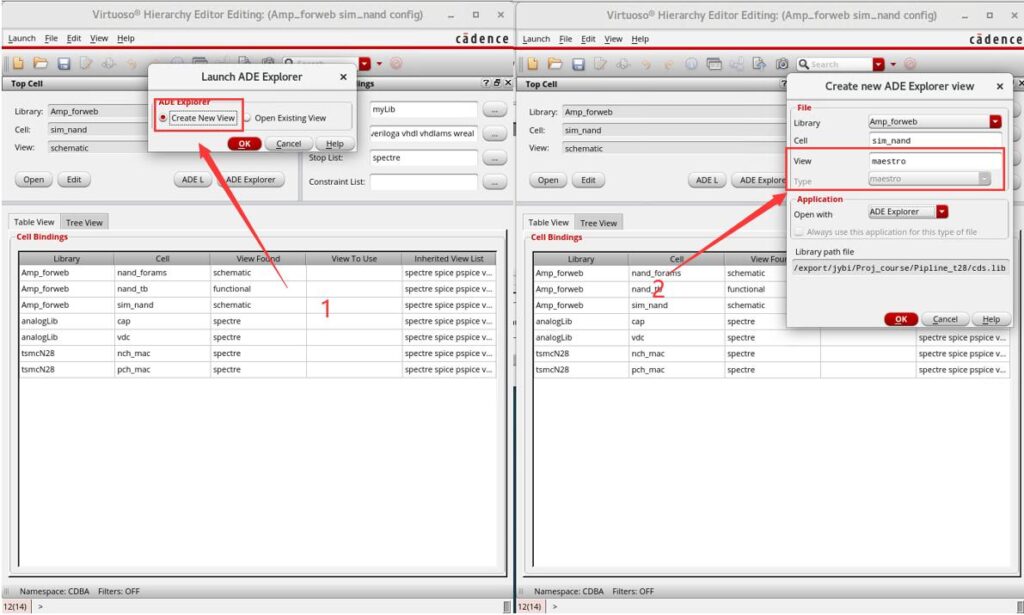

在上文中建好的 config 文件中,选择「ADE Explorer」,即可新建一个 maestro 文件进行仿真,如下图。(如果对 ADE Explorer 不熟悉,大家也可以选择「ADE L」来建立一个 ADE L 仿真环境。)

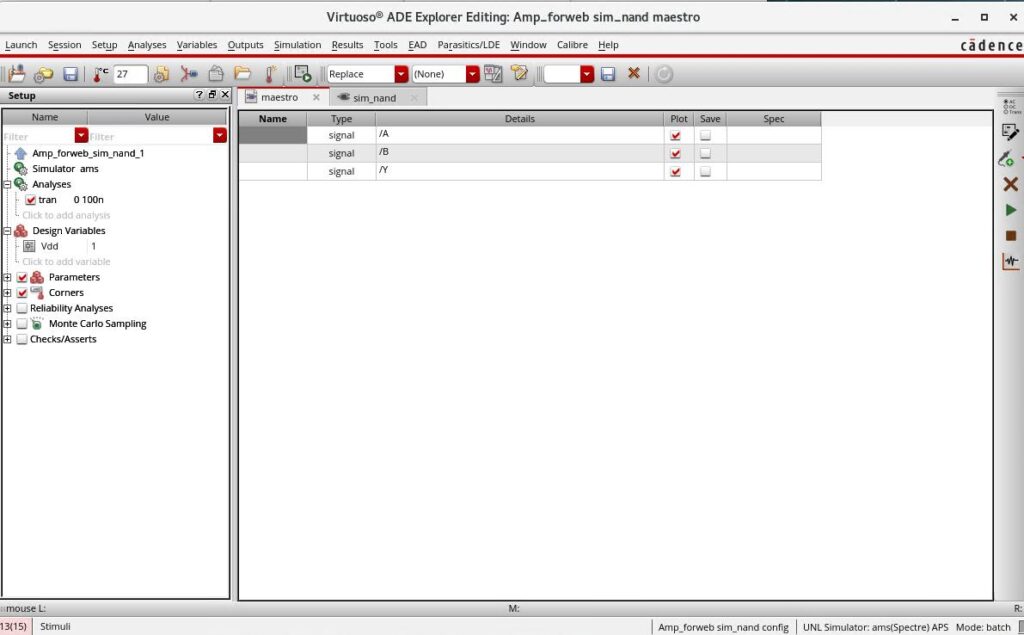

点击 OK 后,Cadence 会自动弹出建好的 maestro 文件,大家这时就可以在 maestro 环境中看到现在使用的仿真器是 ams 仿真器了,如下图:

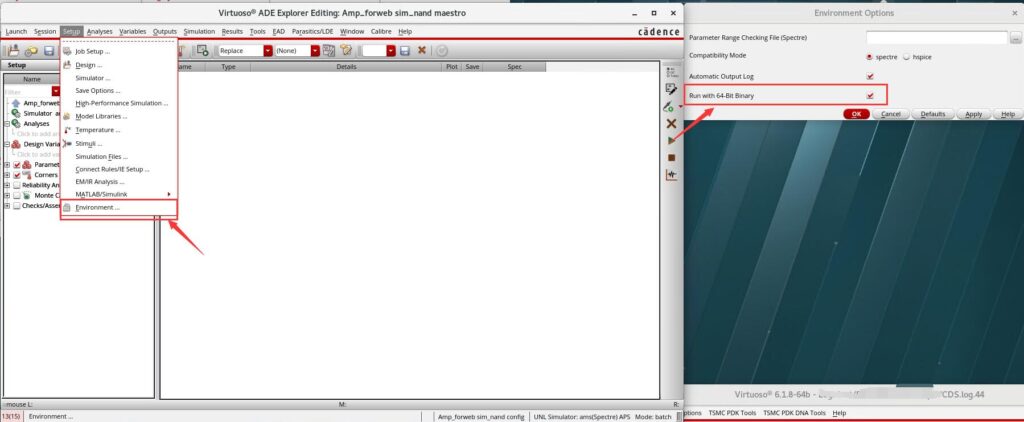

这时大家可以选择「Setup->Environment」选项来设置一下仿真环境,并顺手打开「Run with 64-Bit Binary」选项,如下图:

3.3 设置 Connect Rules 和 IE

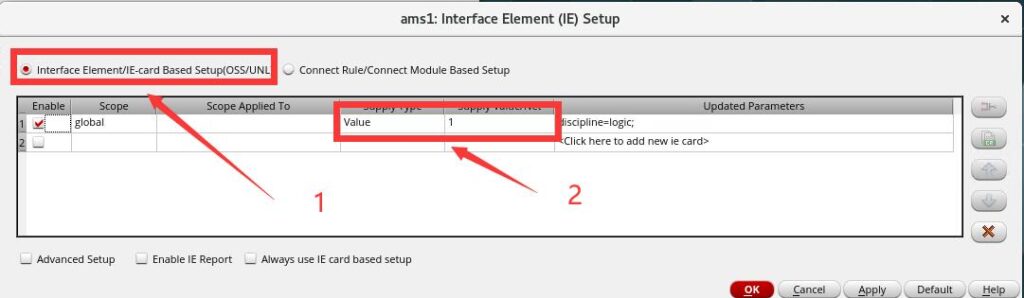

在进行数模混仿前,还需要进行一个 Connect Rules 和 IE 的设置。具体的设置方法为选择「Setup->Connect Rules/IE Setup」选项,这时就可以在弹出的窗口中进行高电平对应的电压值的设置,这里本人以将电源电压设置为 1 V 为例,具体的设置过程如下图。

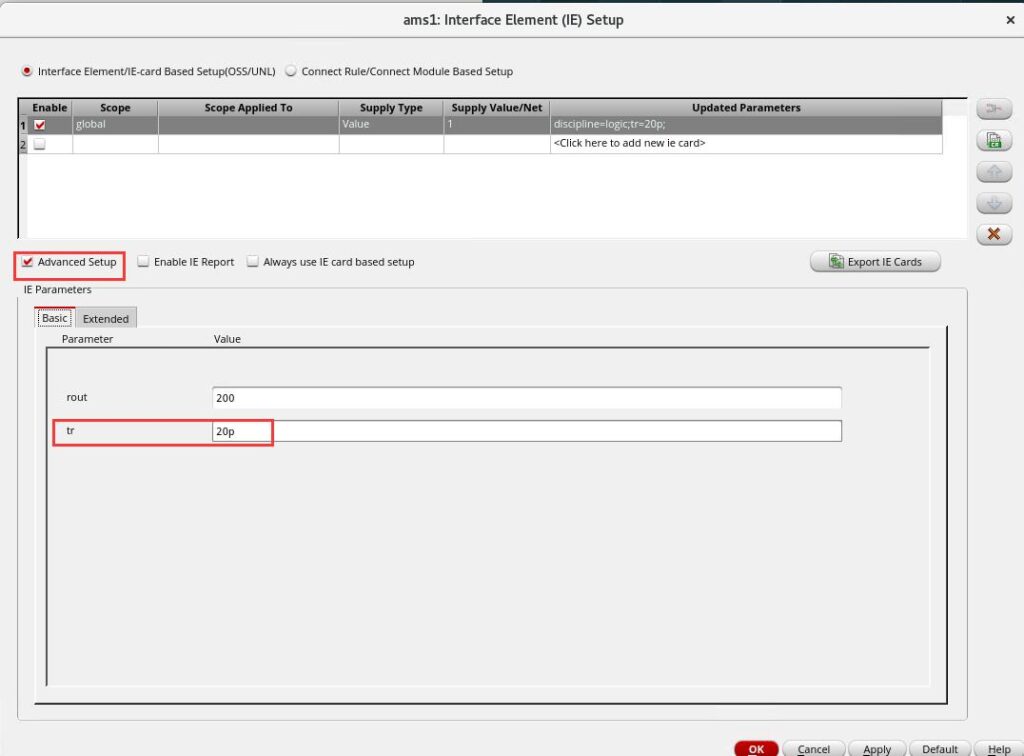

如果你要仿真的电路速度较快,还可以设置数字模块输出的信号的上升时间。在 IE Setup 窗口中选中「Advanced Setup」,就可以进行上升时间 $t_r$ 的设置。这里设置为 20 ps,如下图:

3.4 添加变量、仿真设置与输出,进行数模混仿

上面这些操作都完成后,就可以正常的导入并设置变量,设置仿真类型,并设置输出了。本文将使用一个 100 ns 的 tran 仿真进行演示,并将输出波形设置为 nand 的输入和输出。设置好的 maestro 界面如下图:

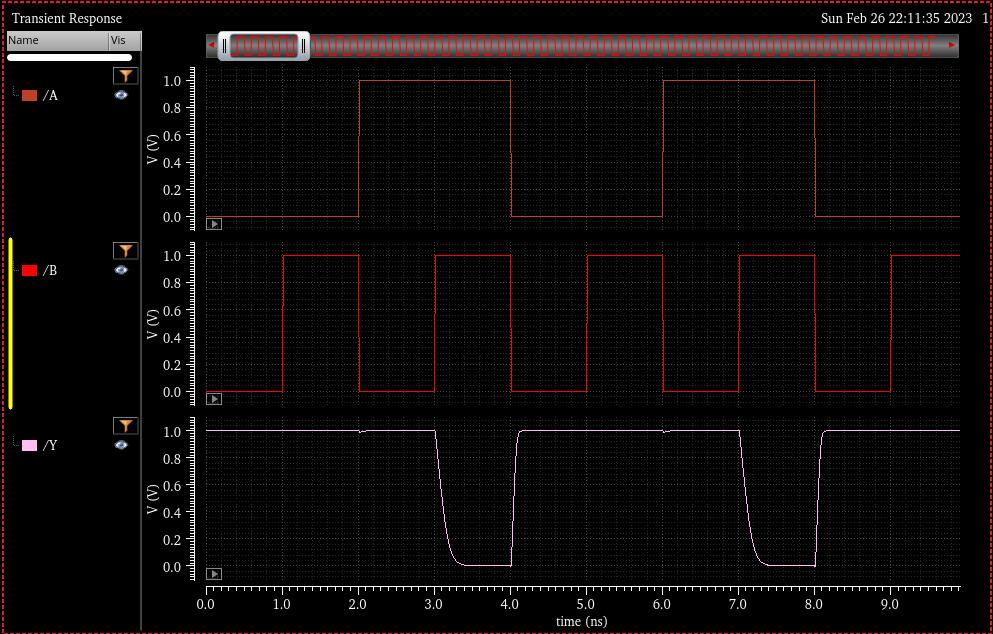

运行仿真,得到的仿真结果如下图所示,可以看出该仿真结果能够体现出一个 nand 的功能。

4 结语

数模混仿是一种将数字电路和模拟电路放在一起进行仿真的一种好方式,但并不是一个很省心的方式。通过上面的描述可以看出,整个数模混仿的流程异常复杂,各种操作较多;同时这些操作如果设置的不正确就可能会造成无法仿真的结果。

此外,AMS 仿真的 bug 也比较多,如果一个 verilog 文件写的有点问题,或者流程中设置的有点问题,就可能会出一个 bug,然后就无法仿真了(并且一般的要找到这个 bug 可能要花费很久的时间)。因此这里我建议,除非必要,大家也可以使用 Verilog-A 来描述一些简单的数字电路模块的功能,这样就可以使用 spectre 仿真器直接进行仿真了,从而避免了某些奇奇怪怪的离谱的 bug。

总之,此文章也只是描述了一种进行数模混仿的通用方法,并不一定适用于所有的服务器环境。大家可能需要根据自己使用的服务器环境酌情进行数模混仿的尝试;如果流程走不通,可能需要去看一下其他的一些博客寻找原因。在这里本人祝大家进行数模混仿时都能不出 bug,流程一遍走通。

请问大佬,有没有对virtuoso的ams混仿比较熟的,有知道:混仿时有里添加了连接的库有L2E这种,但是一个verilog代码的输出没法传输入给另外一个相同代码的输入端口,是没有D -TO-D这种设置吗?本来以为是verilog编译里面irun.log里面有nostdout,但是第一级分频器的输出又能在仿真波形那里看见,我找了几天也没找到解决办法,

事情是这样的:在跑pll混仿的时候,开始都很正常,有一次加了一个新的23分频器的代码之后,就仿不成功了,几个级联的23分频器代码不能连接了,只有第一级23分频器有正确输出,从这之后的分频器在ADE L的仿真波形里都没有输出,导致整个pll环路不能正常工作,卡了好几天实在是不知道怎么改了(可以小偿拜托拜托)

抱歉,这个我这边并不是很了解,我写这篇文章主要是当时需要用到数模混仿,因此记录并分享一下仿真方法,这种复杂的数模混仿我并没有搞过。

你的端口定义是inout吗

不是的,是普通的input和output。

请问我在用AMS仿真的时候想加噪声,勾选了Transient Noise,但是下面没有Multiple Runs的选择框,我没有地方设置仿真次数,请问这个在哪里设置啊?

你好,我这边是有 Multipe Runs 选项的,建议检查一下你的仿真设置或者 spectre 版本,如果仿真设置没问题,可以考虑下载较新的 spectre 版本试一下。

数模混仿后仿真要怎么操作呢?

在 config 中将对应的模块从 schematic 改为 calibre。

但是后仿发现后仿网表无法识别数字信号